Low-power, Small-sized, 1024-SPS, 16-bit, Delta-sigma ADCs

### 1. General Description

The LTD211X family are high-precision, low-power, 16-bit analog-to-digital converters in a small-sized VSSOP-10L package. Oscillator and low-drift voltage reference are integrated internally. LTD2113 and LTD2114 support two single-ended input (or one differential input), while LTD2115 and LTD2118 support up to four single-ended inputs (or two differential inputs), switched by an input multiplexer. LTD2114 and LTD2115 provide a comparator feature for under-voltage and over-voltage detection. LTD2118 provides a precise internal temperature sensor for real-time temperature monitoring.

The LTD211X family supports a conversion rate up to 1024 samples per second (SPS). The integrated programmable gain amplifier (PGA) can modulate the input range from  $\pm 256$  mV to  $\pm 6.144$  V, to be suitable for both large and small input analog signals (LTD2113 excluded, fixed at  $\pm 2.048$  V). LTD2113, LTD2114 and LTD2115 is I²C compatible with four pin-selectable addresses. LTD2118 is SPI compatible.

The LTD211X family performs conversion in either continuous-mode or single-shot mode. The typical supply current value in continuous operation is 150  $\mu$ A. In single-shot mode, the device enters power-down status automatically after the conversion is completed, which significantly suppresses the power consumption during idling. Such features make the LTD211X family appropriate for power sensitive applications such as battery-powered devices.

### 2. Features and Benefits

- Wide voltage supply: 2 V to 5 V

- Low current consumption: 150 μA in continuous operation

- Wide Data rate option: 8 SPS to 1024 SPS

- Single-cycle settling

- Integrated voltage reference

- Integrated oscillator

- I<sup>2</sup>C compatible: four pin-selectable addresses (LTD2113, LTD2114 and LTD2115)

- SPI compatible (LTD2118 only)

- Four single-ended or two differential inputs (LTD2115 and LTD2118)

- Integrated comparator (LTD2114 and LTD2115)

- Integrated temperature sensor (LTD2118 only)

- Small package: 3 mm × 3 mm VSSOP-10L

### 3. Applications

- Temperature measurement system

- Portable instruments

### Low-power, Small-sized, 1024-SPS, 16-bit, Delta-sigma ADCs

- Battery voltage and current monitoring

- Factory automation and process control

- Consumer electronics

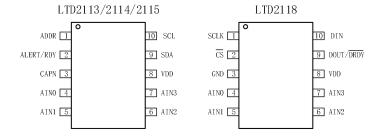

## 4. Pin Configuration (Top View)

### Table of Contents

| 1. General Description          | 1 | 10. Spe |

|---------------------------------|---|---------|

| 2. Features and Benefits        | 1 | 10      |

| 3. Applications                 | 1 | 10      |

| 4. Pin Configuration (Top View) | 2 | 10      |

| Table of Contents               | 2 | 10      |

| 5. Revision History             | 2 | LT      |

| 6. Device Comparison            | 2 | 10      |

| 7. Pin Description              | 3 | 10      |

| 8. Functional Block Diagram     | 3 | 10      |

| 9. Ordering Information         | 3 | 10      |

|                                 |   |         |

| Specifications4                                    |

|----------------------------------------------------|

| 10.1. Limiting Value                               |

| 10.2. ESD Ratings                                  |

| 10.3. Recommended Operating Conditions             |

| 10.4. Characteristics for LTD2113, LTD2114 and     |

| LTD2115                                            |

| 10.5. Timing Requirements: I <sup>2</sup> C        |

| 10.6. Characteristics for LTD2118                  |

| 10.7. Timing Requirements: Serial Interface        |

| 10.8 Switching Characteristics: Social Interface 5 |

### 5. Revision History

#### Version 0

Initial version.

# 6. Device Comparison

| Part Number | Input Channels |              | PGA        | Campanatan | Temperature | lukaufaaa        |  |

|-------------|----------------|--------------|------------|------------|-------------|------------------|--|

|             | Single-ended   | Differential | PGA        | Comparator | Sensor      | Interface        |  |

| LTD2113     | 2              | 1            | NA         | NA         | NA          | I <sup>2</sup> C |  |

| LTD2114     | 2              | 1            | Integrated | Integrated | NA          | I <sup>2</sup> C |  |

| LTD2115     | 4              | 2            | Integrated | Integrated | NA          | I <sup>2</sup> C |  |

| LTD2118     | 4              | 2            | Integrated | NA         | Integrated  | SPI              |  |

# 7. Pin Description

|           |        | Pin N  | ımber  |        |                                                                   |

|-----------|--------|--------|--------|--------|-------------------------------------------------------------------|

| Pin Name  | LTD211 | LTD211 | LTD211 | LTD211 | Description                                                       |

|           | 3      | 4      | 5      | 8      |                                                                   |

| ADDR      | 1      | 1      | 1      | NA     | I <sup>2</sup> C slave address select                             |

| SCLK      | NA     | NA     | NA     | 1      | Serial clock input                                                |

| ALERT/RDY | NA     | 2      | 2      | NA     | Comparator output or conversion ready (LTD2114 and LTD2115 only)  |

| CS        | NA     | NA     | NA     | 2      | Chip select, active low. Connect to GND if not used.              |

| GND       | 3      | 3      | 3      | 3      | Ground                                                            |

| AIN0      | 4      | 4      | 4      | 4      | Analog input 0                                                    |

| AIN1      | 5      | 5      | 5      | 5      | Analog input 1                                                    |

| AIN2      | NA     | NA     | 6      | 6      | Analog input 2                                                    |

| AIN3      | NA     | NA     | 7      | 7      | Analog input 3                                                    |

| VDD       | 8      | 8      | 8      | 8      | Power supply. Connect a 0.1-µF decoupling capacitor to GND.       |

| SDA       | 9      | 9      | 9      | NA     | Serial data. Transmits and receives data                          |

| DOUT/DRDY | NA     | NA     | NA     | 9      | Serial data output combined with data ready indicator, active low |

| SCL       | 10     | 10     | 10     | NA     | Serial clock input, locks data on SDA                             |

| DIN       | NA     | NA     | NA     | 10     | Serial data input                                                 |

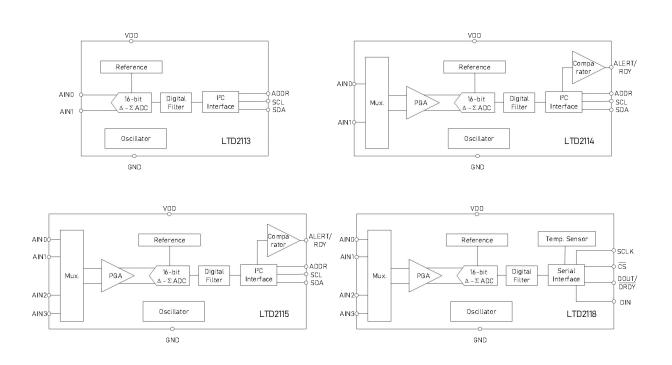

# 8. Functional Block Diagram

# 9. Ordering Information

| Part Number    | Package Type | Quantity            | Mark Code |  |

|----------------|--------------|---------------------|-----------|--|

| LTD2113XV10/R8 | VSSOP-10L    | Tape and Reel, 4000 | D2113     |  |

| LTD2114XV10/R8 | VSSOP-10L    | Tape and Reel, 4000 | D2114     |  |

| LTD2115XV10/R8 | VSSOP-10L    | Tape and Reel, 4000 | D2115     |  |

| LTD2118XV10/R8 | VSSOP-10L    | Tape and Reel, 4000 | D2118     |  |

# 10. Specifications

#### 10.1. Limiting Value

| Parameter                                            | MIN     | MAX     | UNIT       |

|------------------------------------------------------|---------|---------|------------|

| Power supply voltage, VDD to GND                     | -0.3    | 7       | V          |

| Analog input voltage, AINO, AIN1, AIN2, AIN3         | GND-0.3 | VDD+0.3 | V          |

| Digital input voltage, SDA, SCL, ADDR, ALERT/RDY     | GND-0.3 | 5.5     | ٧          |

| Digital input voltage, DIN, DOUT/DRDY, SCLK, CS      | GND-0.3 | VDD+0.3 | V          |

| Input current continuous, any pin except supply pins | -10     | 10      | mA         |

| Operating ambient T <sub>A</sub>                     | -40     | 125     | $^{\circ}$ |

| T <sub>STG</sub>                                     | -60     | 150     | $^{\circ}$ |

#### 10.2. ESD Ratings

| Parameter                                                                 | Level      | UNIT |

|---------------------------------------------------------------------------|------------|------|

| Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins              | $\pm 2000$ | V    |

| Charged device model (CDM), per JEDEC specification JESD22-C101, all pins | ±500       | V    |

#### 10.3. Recommended Operating Conditions

| Parame            | eter                          | Conditions                                              | Min         | Nom | Max         | Unit       |

|-------------------|-------------------------------|---------------------------------------------------------|-------------|-----|-------------|------------|

| Power             | Supply                        |                                                         |             |     |             |            |

|                   | Power supply                  | VDD to GND                                              | 2           |     | 5.5         | ٧          |

| Analog            | Inputs                        |                                                         |             |     |             |            |

| FSR               | Full-scale analog input range | V <sub>IN</sub> = V <sub>AINP</sub> - V <sub>AINN</sub> | $\pm$ 0.256 |     | $\pm$ 6.144 | ٧          |

| V <sub>AINX</sub> | Absolute input voltage        |                                                         | GND         |     | VDD         | ٧          |

| Digital           | Inputs                        |                                                         |             |     |             |            |

|                   | Input voltage                 | LTD2113, LTD2114, LTD2115                               | GND         |     | 5.5         | ٧          |

|                   | Input voltage                 | LTD2118                                                 | GND         |     | VDD         | ٧          |

| Tempe             | rature                        |                                                         |             |     |             |            |

| T <sub>A</sub>    | Ambient temperature           |                                                         | -45         |     | 125         | $^{\circ}$ |

### 10.4. Characteristics for LTD2113, LTD2114 and LTD2115

Minimum and maximum specifications are measured from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are measured at  $T_A = 25^{\circ}\text{C}$ ; all specifications are measured at VDD = 3.3 V, AVSS = 0 V, data rate = 8 SPS, FSR = 2.048 V (unless otherwise noted).

| Parameter                    | Conditions                               | Min | Тур  | Max | Unit |  |

|------------------------------|------------------------------------------|-----|------|-----|------|--|

| Analog Inputs                |                                          | _   |      |     |      |  |

|                              | FSR = ±6.144 V                           |     | 10   |     |      |  |

| 0                            | FSR = $\pm$ 4.096 V, FSR = $\pm$ 2.048 V |     | 6    |     |      |  |

| Common-mode input impedance  | FSR = ±1.024 V                           |     | 3    |     | МΩ   |  |

|                              | FSR = $\pm$ 0.512 V, FSR = $\pm$ 0.256 V |     | 100  |     |      |  |

|                              | FSR = ±6.144 V                           |     | 22   |     |      |  |

|                              | FSR = ±4.096 V                           |     | 15   |     |      |  |

| Differential input impedance | FSR = ±2.048 V                           |     | 4.9  |     | МΩ   |  |

|                              | FSR = ±1.024 V                           |     | 2.4  | ,   | 1    |  |

|                              | FSR = $\pm$ 0.512 V, FSR = $\pm$ 0.256 V |     | 0.71 |     | ]    |  |

### LTD211X Series

# Low-power, Small-sized, 1024-SPS, 16-bit, Delta-sigma ADCs

| Perform         |                               | T.,                                                              |            |                 | -          |       |

|-----------------|-------------------------------|------------------------------------------------------------------|------------|-----------------|------------|-------|

|                 | Resolution                    | No missing code                                                  | 16         |                 |            | Bits  |

| DR              | Data rate                     |                                                                  | 8, 16, 32  | , 64, 128, 256, | 512, 1024  | SPS   |

|                 | Data rate variation           |                                                                  | -10%       |                 | +10%       |       |

| INL             | Integral non-linearity        | DR = 8 SPS, FSR = $\pm 2.048$ V                                  |            |                 | 1          | LSB   |

|                 | Offset error                  | FSR = $\pm$ 2.048 V, differential inputs                         | -3         | ±1              | 3          | LSB   |

|                 | onset error                   | FSR = $\pm$ 2.048 V, single-ended inputs                         |            | $\pm 3$         |            | LJB   |

|                 | Offset drift                  | FSR = $\pm$ 2.048 V, T <sub>A</sub> = -40 to 125 $^{\circ}$ C    |            | 0.005           | _          | LSB/℃ |

|                 | Offset long-term drift        | FSR = $\pm$ 2.048 V, T <sub>A</sub> = 125 $^{\circ}$ C, 1000 hrs |            | ±1              |            | LSB   |

|                 | Offset power supply rejection | FSR = $\pm$ 2.048 V, DC supply variation                         |            | 1               |            | LSB/V |

|                 | Offset channel match          | Match between any two inputs                                     |            | 3               |            | LSB   |

|                 | Gain effor                    | FSR = $\pm$ 2.048 V, T <sub>A</sub> = 25 $^{\circ}$ C            |            | 0.01%           | 0.15%      |       |

|                 |                               | FSR = ±0.256 V                                                   |            | 7               |            |       |

|                 | Gain drift                    | FSR = ±2.048 V                                                   |            | 5               | 40         | ppm/℃ |

|                 |                               | FSR = ±6.144 V                                                   |            | 5               |            |       |

|                 | Gain match                    | Match between any two gains                                      |            | 0.02%           | 0.1%       |       |

|                 | Gain channel match            | Match between any two inputs                                     |            | 0.05%           | 0.1%       |       |

|                 | Gain long-term drift          | FSR = $\pm 2.048$ V, $T_A$ = 125 $^{\circ}$ C, 1000 hrs          |            | ±0.05%          |            |       |

|                 | <u> </u>                      | DC, FSR = ±0.256 V                                               |            | 105             |            | dB    |

|                 |                               | DC, FSR = ±2.048 V                                               |            | 100             |            |       |

| CMRR            | Common-mode rejection ratio   | DC, FSR = ±6.144 V                                               |            | 90              |            |       |

|                 | •                             | f <sub>CM</sub> = 60Hz, DR = 8 SPS                               |            | 105             | •          |       |

|                 |                               | f <sub>CM</sub> = 50Hz, DR = 8 SPS                               |            | 105             |            |       |

| Digital II      | nputs / Outputs               | •                                                                | •          |                 |            |       |

| V <sub>OL</sub> | Low-level output voltage      | I <sub>OL</sub> = 3 mA                                           | GND        | 0.15            | 0.4        | ٧     |

| V <sub>IL</sub> | Low-level input voltage       |                                                                  | GND        |                 | 0.3 × DVDD | ٧     |

| V <sub>IH</sub> | High-level input voltage      |                                                                  | 0.7 × DVDD |                 | 5.5        | ٧     |

|                 | Input leakage                 |                                                                  | -10        |                 | 10         | μА    |

| Power S         | iupply                        | •                                                                | •          |                 |            |       |

|                 |                               | Power down                                                       |            | 0.5             | 2          |       |

| $I_{VDD}$       | Supply current                | Operating-continuous                                             |            | 150             | 200        | mA    |

|                 |                               | VDD = 5 V                                                        |            | 0.9             |            |       |

| PD              | Power dissipation             | VDD = 3.3 V                                                      |            | 0.5             |            | mW    |

|                 | ·                             | VDD = 2 V                                                        |            | 0.3             |            | ••    |

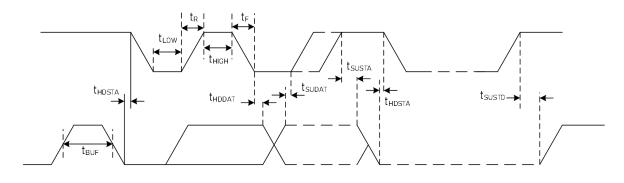

## 10.5. Timing Requirements: I<sup>2</sup>C

Over operating ambient temperature range and VDD = 2.0 V to 5.5 V (unless otherwise noted)

| D                  |                                                                                      |      | mode | High-spe | LINUT |      |

|--------------------|--------------------------------------------------------------------------------------|------|------|----------|-------|------|

| Parameter          |                                                                                      | MIN  | MAX  | MIN      | MAX   | UNIT |

| f <sub>SCL</sub>   | SCL clock frequency                                                                  | 0.01 | 0.4  | 0.01     | 3.4   | MHz  |

| t <sub>BUF</sub>   | Bus free time between START and STOP condition                                       | 600  |      | 160      |       | ns   |

| t <sub>HDSTA</sub> | Hold time after repeated START condition. First clock is generated after this period | 600  |      | 160      |       | ns   |

| t <sub>susto</sub> | Setup time for STOP condition                                                        | 600  |      | 160      |       | ns   |

| t <sub>HDDAT</sub> | Data hold time                                                                       | 0    |      | 0        |       | ns   |

| t <sub>SUDAT</sub> | Data setup                                                                           | 100  |      | 10       |       | ns   |

| $t_{LOW}$          | Low period of the SCL clock pin                                                      | 1300 |      | 160      |       | ns   |

| t <sub>HIGH</sub>  | High period of the SCL clock pin                                                     | 600  |      | 60       |       | ns   |

| t <sub>F</sub>     | Rise time for both SDA and SCL signals                                               |      | 300  | ·        | 160   | ns   |

| t <sub>R</sub>     | Fall time for both SDA and SCL signals                                               |      | 300  |          | 160   | ns   |

### Low-power, Small-sized, 1024-SPS, 16-bit, Delta-sigma ADCs

I<sup>2</sup>C Interface Timing

#### 10.6. Characteristics for LTD2118

Minimum and maximum specifications are measured from  $T_A = -40^{\circ}\text{C}$  to +125°C; typical specifications are measured at  $T_A = 25^{\circ}\text{C}$ ; all specifications are measured at VDD = 3.3 V, AVSS = 0 V, data rate = 8 SPS, FSR = 2.048 V (unless otherwise noted).

| Paramet  | ter                           | Conditions                                            | Min       | Тур                | Max      | Unit |

|----------|-------------------------------|-------------------------------------------------------|-----------|--------------------|----------|------|

| Analog I | nputs                         |                                                       |           |                    |          |      |

|          |                               | FSR = ±6.144 V                                        |           | 8                  |          |      |

|          | C                             | FSR = $\pm$ 4.096 V, FSR = $\pm$ 2.048 V              |           | 6                  |          |      |

|          | Common-mode input impedance   | FSR = ±1.024 V                                        |           | 3                  |          | МΩ   |

|          |                               | FSR = $\pm$ 0.512 V, FSR = $\pm$ 0.256 V              |           | 100                |          |      |

|          |                               | FSR = ±6.144 V                                        |           | 22                 |          |      |

|          |                               | FSR = ±4.096 V                                        |           | 15                 |          |      |

|          | Differential input impedance  | FSR = ±2.048 V                                        |           | 4.9                |          | МΩ   |

|          |                               | FSR = ±1.024 V                                        |           | 2.4                |          |      |

|          |                               | FSR = $\pm$ 0.512 V, FSR = $\pm$ 0.256 V              |           | 0.71               |          |      |

| Perform  | ance                          |                                                       |           |                    |          |      |

|          | Resolution                    | No missing code                                       | 16        |                    |          | Bits |

| DR       | Data rate                     |                                                       | 8, 16, 32 | 2, 64, 128, 256, 5 | 12, 1024 | SPS  |

|          | Data rate variation           |                                                       | -10%      |                    | +10%     |      |

| INL      | Integral non-linearity        | DR = 8 SPS, FSR = ±2.048 V                            |           |                    | 1        | LSE  |

|          | Offset error                  | FSR = $\pm$ 2.048 V, differential inputs              |           | ± 0.1              | 2        | LSB  |

|          |                               | FSR = $\pm 2.048$ V, single-ended inputs              |           | ±0.25              |          |      |

|          | Offset drift                  | FSR = ±2.048 V, T <sub>A</sub> = -40 to 125 °C        |           | 0.002              |          | LSB/ |

|          | Offset long-term drift        | FSR = ±2.048 V, T <sub>A</sub> = 125 °C, 1000 hrs     |           | ±1                 |          | LSE  |

|          | Offset power supply rejection | FSR = $\pm 2.048$ V, DC supply variation              |           | 0.2                |          | LSB/ |

|          | Offset channel match          | Match between any two inputs                          |           | 0.6                |          | LSE  |

|          | Gain effor                    | FSR = $\pm 2.048$ V, T <sub>A</sub> = 25 $^{\circ}$ C |           | 0.01%              | 0.15%    |      |

|          |                               | FSR = ±0.256 V                                        |           | 7                  |          |      |

|          | Gain drift                    | FSR = ±2.048 V                                        |           | 5                  | 40       | ppm/ |

|          |                               | FSR = ±6.144 V                                        |           | 5                  |          |      |

|          | Gain power supply rejection   |                                                       |           | 10                 |          | ppm/ |

|          | Gain match                    | Match between any two gains                           |           | 0.01%              | 0.1%     |      |

|          | Gain channel match            | Match between any two inputs                          |           | 0.01%              | 0.1%     |      |

|          |                               | DC, FSR = ±0.256 V                                    |           | 105                |          |      |

|          |                               | DC, FSR = ±2.048 V                                    |           | 100                |          | 7    |

| CMRR     | Common-mode rejection ratio   | DC, FSR = ±6.144 V                                    |           | 90                 |          | dB   |

|          |                               | f <sub>CM</sub> = 60Hz, DR = 8 SPS                    |           | 105                |          | 7    |

|          |                               | f <sub>CM</sub> = 50Hz, DR = 8 SPS                    |           | 105                |          | ┪    |

#### Digital Inputs / Outputs

# LTD211X Series

### Low-power, Small-sized, 1024-SPS, 16-bit, Delta-sigma ADCs

| $V_{\text{oL}}$  | Low-level output voltage  | I <sub>0L</sub> = 1 mA  | GND       |         | 0.2 × VDD | ٧          |

|------------------|---------------------------|-------------------------|-----------|---------|-----------|------------|

| V <sub>он</sub>  | High-level output voltage | I <sub>он</sub> = 1 mA  | 0.8 × VDD |         |           | ٧          |

| V <sub>IL</sub>  | Low-level input voltage   |                         | GND       |         | 0.2 × VDD | ٧          |

| I <sub>H</sub>   | Input leakage, high       | V <sub>IH</sub> = 5.5 V | -10       |         | 10        | μА         |

| Iι               | Input leakage, low        | V <sub>IL</sub> = GND   | -10       |         | 10        | μА         |

| Tempe            | ature Sensor              | •                       |           |         |           | •          |

|                  | Operating range           |                         | -40       |         | 125       | $^{\circ}$ |

|                  | Temperature resolution    |                         |           | 0.03125 |           | ℃/LSB      |

|                  | Accuracy                  |                         |           | 0.4     | ±1        | °C         |

| Power            | Supply                    | •                       |           |         |           |            |

|                  | Supply current            | Power down              |           | 0.5     | 2         | mA         |

| I <sub>VDD</sub> |                           | Operating-continuous    |           | 150     | 200       |            |

|                  | Power dissipation         | VDD = 5 V               |           | 0.9     |           | mW         |

| PD               |                           | VDD = 3.3 V             |           | 0.5     |           |            |

|                  |                           | VDD = 2 V               |           | 0.3     | •         |            |

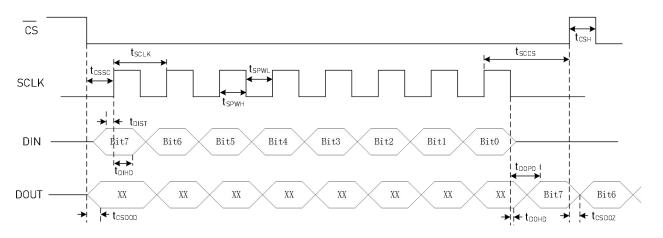

### 10.7. Timing Requirements: Serial Interface

P-7

Over operating ambient temperature range and VDD = 2.0 V to 5.5 V (unless otherwise noted)

| Parameter                             |                                                                       | MIN | MAX | UNIT |

|---------------------------------------|-----------------------------------------------------------------------|-----|-----|------|

| t <sub>cssc</sub>                     | Delay time, first SCLK rising edge after $\overline{CS}$ falling edge | 100 |     | ns   |

| t <sub>DIST</sub>                     | Setup time, DIN valid before SCLK falling edge                        | 50  |     | ns   |

| t <sub>DIHD</sub>                     | Hold time, DIN valid after SCLK falling edge                          | 50  |     | ns   |

| t <sub>SCLK</sub>                     | SCLK period                                                           | 250 |     | ns   |

| t <sub>SPWL</sub> , t <sub>SPWH</sub> | Pulse duration, SCLK high or low                                      | 100 |     | ns   |

| t <sub>sccs</sub>                     | Delay time, last SCLK falling edge before CS rising edge              | 100 |     | ns   |

| t <sub>CSH</sub>                      | Pulse duration, CS high                                               | 200 |     | ns   |

| t <sub>DOHD</sub>                     | Hold time, SCLK rising edge to DOUT invalid                           | 0   | _   | ns   |

### 10.8. Switching Characteristics: Serial Interface

Over operating ambient temperature range, load: 20 pF || 100 k $\!\Omega$  to GND.

| Parameter          |                                                               | MIN | TYP | MAX | UNIT |

|--------------------|---------------------------------------------------------------|-----|-----|-----|------|

| tcsDOD             | Propagation delay time, CS falling edge to DOUT driven        | 0   |     | 50  | ns   |

| t <sub>DOPD</sub>  | Propagation delay time, SCLK rising edge to valid DOUT        |     |     | 40  | ns   |

| t <sub>CSDOZ</sub> | Propagation delay time, CS rising edge to DOUT high impedance |     |     | 50  | ns   |

Serial Interface Timing